# 6V Input, 1A, ACOT<sup>®</sup> Buck Converter in Thin SOT-563 (FC)

### **General Description**

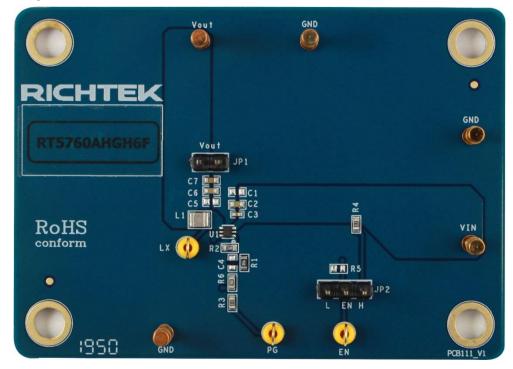

The RT5760A is a full featured 6V, 1A, Advanced Constant-On-Time (ACOT<sup>®</sup>) synchronous step-down converter with two integrated MOSFETs. This document explains the function and use of the RT5760A evaluation board (EVB) and provides information for the evaluation board layout, schematic, bill of materials (BOM) and measurement results to suit individual requirements.

## **Table of Contents**

| General Description                           | 1  |

|-----------------------------------------------|----|

| Performance Specification Summary             | 2  |

| Power-up Procedure                            | 2  |

| Detailed Description of Hardware              | 3  |

| Bill of Materials                             | 5  |

| Typical Applications                          | 6  |

| Evaluation Board Layout                       | 11 |

| More Information                              | 13 |

| Important Notice for Richtek Evaluation Board | 13 |

### **Performance Specification Summary**

Summary of the RT5760AHGH6F Evaluation Board performance specificiaiton is provided in Table 1. The ambient temperature is 25°C.

| Table 1. | RT5760AHGH6F | Evaluation | Board | Performance | Specification | Summary |

|----------|--------------|------------|-------|-------------|---------------|---------|

|          |              |            |       |             |               |         |

| Specification           | Test Conditions                          | Min | Тур  | Max | Unit  |

|-------------------------|------------------------------------------|-----|------|-----|-------|

| Input Voltage Range     |                                          | 2.5 |      | 6   | V     |

| Output Current          |                                          | 0   |      | 1   | А     |

| Default Output Voltage  |                                          |     | 1    |     | V     |

| Operation Frequency     |                                          |     | 2.2  |     | MHz   |

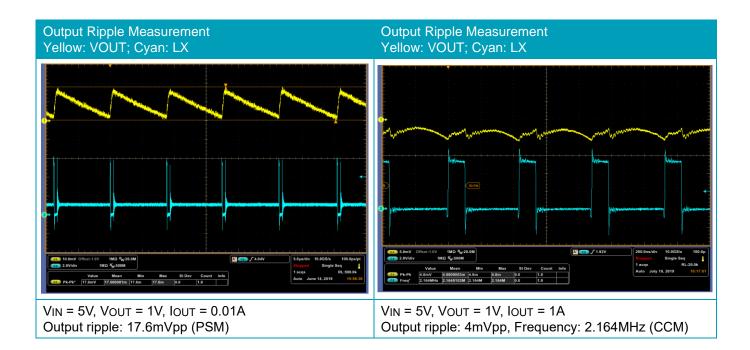

| Output Ripple Voltage   | IOUT = 1A                                |     | 10   |     | mVp-p |

| Line Regulation         | $I_{OUT} = 1A$ , $V_{IN} = 2.5V$ to $6V$ |     | ±1   |     | %     |

| Load Regulation         | VIN = 5V, IOUT = 0.001A to 1A            |     | ±1   |     | %     |

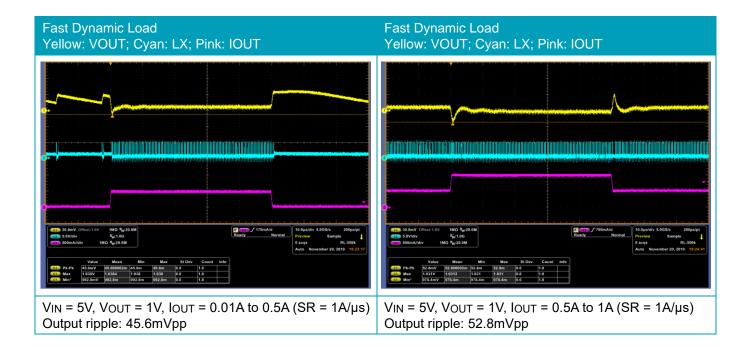

| Load Transient Response | IOUT = 0A to 1A                          |     | ±5   |     | %     |

| Efficiency              | VIN = 5V, VOUT = 1V, IOUT = 0.4A         |     | 85.8 |     | %     |

### **Power-up Procedure**

#### **Suggestion Required Equipments**

- RT5760AHGH6F Evaluation Board

- DC power supply capable of at least 6V and 1A

- Electronic load capable of 1A

- Function Generator

- Oscilloscope

### **Quick Start Procedures**

The Evaluation Board is fully assembled and tested. Follow the steps below to verify board operation. Do not turn on supplies until all connections are made. When measuring the output voltage ripple, care must be taken to avoid a long ground lead on the oscilloscope probe. Measure the output voltage ripple by touching the probe tip and ground ring directly across the last output capacitor.

### Proper measurement equipment setup and follow the procedure below.

- 1) With power off, connect the input power supply to VIN and GND pins.

- 2) With power off, connect the electronic load between the VOUT and nearest GND pins.

- 3) Turn on the power supply at the input. Make sure that the input voltage does not exceeds 60V on the Evaluation Board.

- 4) Check for the proper output voltage using a voltmeter.

- 5) Once the proper output voltage is established, adjust the load within the operating ranges and observe the output voltage regulation, ripple voltage, efficiency and other performance.

### **Detailed Description of Hardware**

### **Headers Description and Placement**

Carefully inspect all the components used in the EVB according to the following Bill of Materials table, and then make sure all the components are undamaged and correctly installed. If there is any missing or damaged component, which may occur during transportation, please contact our distributors or e-mail us at <u>evb\_service@richtek.com</u>.

### **Test Points**

The EVB is provided with the test points and pin names listed in the table below.

| Test Point | Signal                    | Comment (expected waveforms or voltage levels on test points)                                                        |

|------------|---------------------------|----------------------------------------------------------------------------------------------------------------------|

| VIN        | Input Voltage             | Positive input voltage from the power supply to the EVB.                                                             |

| VOUT       | Output Voltage            | Positive output voltage from the EVB to the loads.                                                                   |

| JP1        | Output Voltage Test Point | Output voltage measurement point.                                                                                    |

| GND        | Ground                    | Reference voltage for input voltage, output voltage and other test points.                                           |

| LX         | Switch Node Test Point    | Frequency measurement point. 2.2MHz (Typ.) in CCM mode.                                                              |

| PG         | Power Good Test Point     | Power good indicator. Pull low for fault condition.                                                                  |

| EN         | Enable Test Point         | Enable control input. Connect this pin to logic high to enable the device.                                           |

| JP2        | EN Pin Jumper             | Place the jumper across on EN and H to enable the device. Place the jumper across on EN and L to disable the device. |

#### **Power-up & Measurement Procedure**

- 1. Connect a input power supply to the VIN and GND terminals and an electrical load to the VOUT and GND terminals.

- 2. Set the jumper at JP2 to tie "EN" test pin to "H" pin for enabling the chip.

- 3. Apply a 5V nominal input power supply  $(2.5V < V_{IN} < 6V)$  to the VIN and GND terminals respectively.

- 4. Set the electrical load up to 1A to Verify the output voltage (approximately 1V) at JP1. Check LX frequency is around 2.2MHz in CCM mode.

### **Output Voltage Setting**

Set the output voltage with the resistive divider (R1, R2) between VOUT and GND with the midpoint connected to FB. The output is set by the following formula :

VOUT =

$$0.6 \times (1 + \frac{R1}{R2})$$

The placement of the resistive divider should be within 5mm of the FB pin. The resistance of R2 is suggested to  $10k\Omega$  for noise pick-up at the FB pin. The resistance of R1 can then be obtained as below :

R1 =

$$\frac{\text{R2} \times (\text{V}_{\text{OUT}} - 0.6)}{0.6}$$

For better output voltage accuracy, divider resistors (R1 and R2) should have tolerance of ±1% tolerance or better.

# RT5760AHGH6F Evaluation Board

## **Bill of Materials**

| Reference  | Qty | Part Number         | Description                  | Package | Manufacturer |

|------------|-----|---------------------|------------------------------|---------|--------------|

| U1         | 1   | RT5760AHGH6F        | Step-Down<br>DC-DC Converter | SOT-563 | WALSIN       |

| C1, C4, C5 | 3   |                     | NC                           | C-0603  |              |

| C2, C6     | 2   | 0603X106M6R3CT      | 10µF/6.3V/X5R/0603           | C-0603  | WALSIN       |

| C3         | 1   | C1005X7R1C104K050BC | 100nF/16V/X7R/0402           | C-0402  | TDK          |

| C7         | 1   | C1608X7R1H104K080AA | 100nF/50V/X7R/0603           | C-0603  | TDK          |

| L1         | 1   | DFE252010F-1R0M     | 1µH                          | L-2520  | Murata       |

| R1         | 1   | WR06X6651FTL        | 6.65K/0603                   | R-0603  | WALSIN       |

| R2         | 1   | WR06X1002FTL        | 10K/0603                     | R-0603  | WALSIN       |

| R3, R4     | 2   | WR06X1003FTL        | 100K/0603                    | R-0603  | WALSIN       |

| R5         | 1   |                     | NC                           | R-0603  |              |

| R6         | 1   | WR06X000 PTL        | 0/0603                       | R-0603  | WALSIN       |

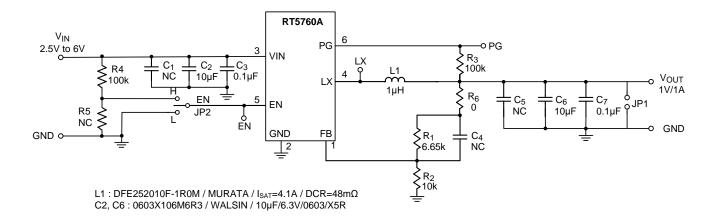

## **Typical Applications**

### **EVB Schematic Diagram**

Note:

Do not hot-plug a live 5V supply to the board. If hot-plugging is required, add ~ 100μF electrolytic capacitor at the input.

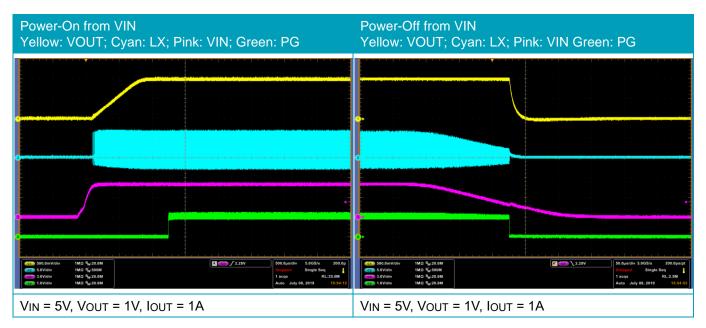

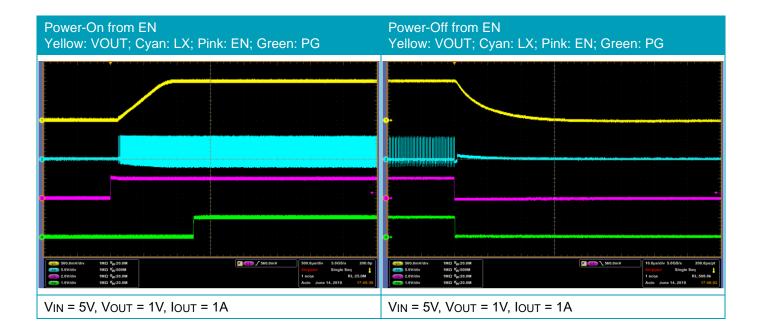

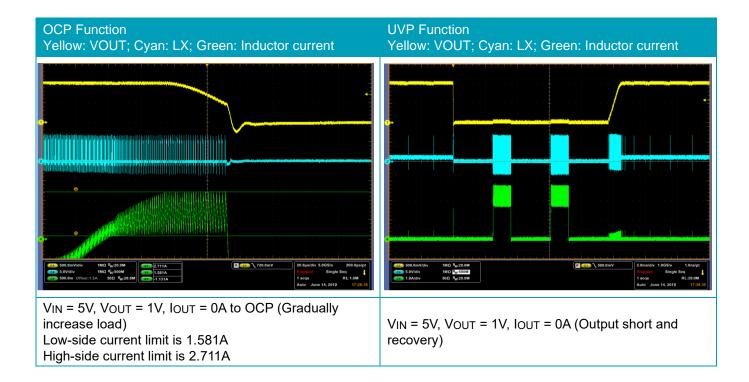

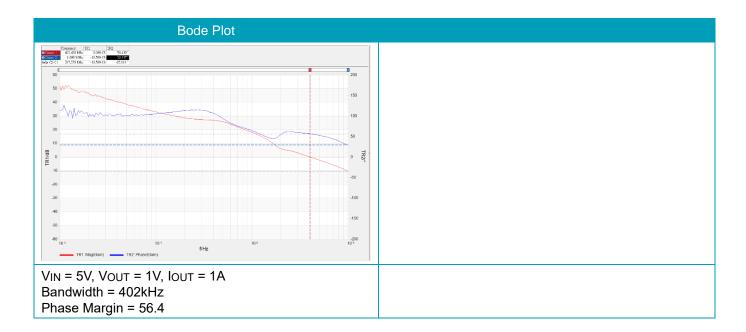

### **Measurement Results**

# RT5760AHGH6F Evaluation Board

# RT5760AHGH6F Evaluation Board

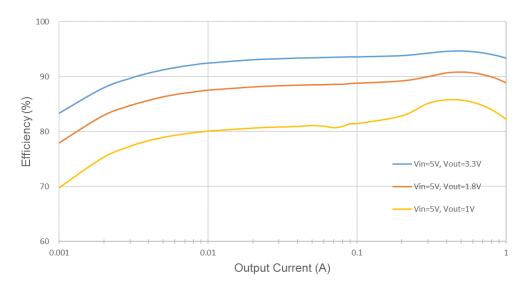

### **Efficiency Measurements**

Efficiency vs. Output Current

## Evaluation Board Layout

• GND • Vout . GND . LABEL Vout JP 1 . VIN :**E** 🗍 R5 JP2 0 0 14 • GND • PG ΕN

Figure 1. Top View (1<sup>st</sup> layer)

Figure 2. PCB Layout—Inner Side (2<sup>nd</sup> Layer)

# RT5760AHGH6F Evaluation Board

| $\mathbf{O}$ | • |   | 0 |

|--------------|---|---|---|

|              | ٥ | 0 | • |

| 0 0          |   | Ð |   |

| 0 0          |   | 0 | • |

| 0 0          | • | * | ٠ |

| 0            |   | 0 | 0 |

Figure 3. PCB Layout—Inner Side (3<sup>rd</sup> Layer)

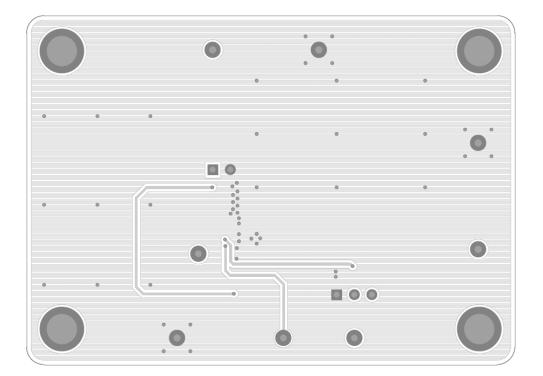

Figure 4. Bottom View (4<sup>th</sup> Layer)

### More Information

For more information, please find the related datasheet or application notes from Richtek website <u>http://www.richtek.com</u>.

## Important Notice for Richtek Evaluation Board

THIS DOCUMENT IS FOR REFERENCE ONLY, NOTHING CONTAINED IN THIS DOCUMENT SHALL BE CONSTRUED AS RICHTEK'S WARRANTY, EXPRESS OR IMPLIED, UNDER CONTRACT, TORT OR STATUTORY, WITH RESPECT TO THE PRESENTATION HEREIN. IN NO EVENT SHALL RICHTEK BE LIABLE TO BUYER OR USER FOR ANY AND ALL DAMAGES INCLUDING WITHOUT LIMITATION TO DIRECT, INDIRECT, SPECIAL, PUNITIVE OR CONSEQUENTIAL DAMAGES.